撰文:Rick

2023 年8 月的最後幾天,劉燁明顯感覺到晶片部門的氣氛變得有些不同。

“ 同事開始喊著這次要強勢歸來”,樂觀的氣氛蔓延到了整個華為內部。

全員沸騰的時刻在29 日中午進入了高點,劉燁發現朋友圈罕見的被同事刷屏——華為在自己的官方商城毫無預告的上架了新款旗艦手機Mate 60 pro 。

而人們最關心的是:Mate 60 pro 所搭載的麒麟9000s,到底是怎麼來的?

馬上就是麒麟9000 的生日了,我們想在此之前,跟大家講述一下它的下一代芯片麒麟9000s 的故事,這是一個鼓舞人心的故事。

為此,知危編輯部找到了半導體產業相關人士、華為的前員工、供應鏈上下游企業人士,希望能獲得一些答案,感謝他們在有限的範圍裡盡可能坦誠地分享,讓我們得以盡可能準確的窺見晶片產業過去三年的發展路徑。

在其中,知危感受到的,不只是華為,而是整個產業鏈在為了共同的目標協同進發,完成這個結果。

代號,夏洛特

其實,自麒麟計畫啟動起,不少晶片就是交錯研發的。

例如麒麟920 和麒麟910,幾乎是並行開發和交付的,這種方式在內部被稱為 “ 擰毛巾模式”。

那麼,依照慣例,麒麟9000 在2020 年量產時,應該已有並行的新專案處於開發狀態。

知危所聯繫的晶片產業相關人士吳旭對8 月30日購買得到的華為Mate60 pro 進行了拆機,並且對晶片進行了Decap(開封)。

進行Decap 除了觀察分析晶片的內部結構,也是為了尋找麒麟9000s 的真實量產日期。先前,網路上盛傳晶片外殼上的「 2035CN 」 代表晶片是在2020 年第35 週生產,但他認為這個資訊的參考價值不大,更像是某種混淆視聽的「 偽裝」。

吳旭透過酸洗放大後得到了一個特殊的編碼“ 2017 ”,經過幾方求證,他認為這是TO( Tape-out )日期,也就是集成電路( IC )或印刷電路板( PCB )設計的最後步驟的日期,一般來講,這個數字出現在晶片金屬層的第13~15 層。

而「 2017 」 的意思是,2020 年第17 週。

一般地,晶片會在定稿後100~200 天開始進行量產,所以,該人士認為,手中這片麒麟9000s 的真實生產日期為:2021 年初。

晶片量產前要經過四個階段,設計階段、開發階段、試產階段和量產階段。流片往往是晶片製造中最重要、最燒錢的環節,有晶片廠曾估算7nm 製程一次流片要3,000 萬美元。而這個過程至少持續三個月( 包括原料準備、光刻、摻雜、電鍍、封裝測試),要經過1000 多道工藝,生產週期較長。

結合流片時間和該枚晶片的生產日期,該人士判斷麒麟9000s 的立項時間至少不晚於2020 年,並且一開始就以不在台積電( TSMC )進行生產為目的。

另外一位華為員工向知危證實,麒麟9000s 的立項生產時間在一年半左右,時間“ 大概19 年末”, 並且在設計階段耗費了一些精力。

該人士稱,海思和其他晶片設計廠不同的地方在於,「 基本上都會做DTCO( 電路設計與製程協同優化),並且下放到晶體管層面的細節,不只做單純的佈線。」這樣做的好處是性能更好,缺點在於需要更長的時間和更高的技術設計。

「 例如正常設計的密度和性能是95%,經過DTCO 的優化,可能達到100% 或更好,但是很費時間,還需要和fab 廠商設計協同。各晶片設計廠可以做,但基本上不做,高通有時候做一些。”

根據其掌握的消息,麒麟9000s 內部曾有版本稱為Hi36b0 。 Hi 代表華為海思,36 代表麒麟旗艦產品線,b0 代表第十一代。在這次晶片的量產中,則是採用了新的標識,也就是Hi36a0V120 而不是「 b0 」。後面的「 V120 」 中的2 和0 代表版本更改和小的優化迭代數字( V 後面的1 在其他華為晶片上指產品代數,例如電視機的晶片第一代是V100第二代是V200,但在Hi36 麒麟系列上暫不確定其意義)。

除了這串代號,麒麟9000s 在內部還有一個更容易記住的名字,夏洛特,美國城市名。

麒麟晶片雖然以中國神話神獸為稱,但是具體型號在內部一直以美國城市命名。上一代麒麟9000 為巴爾的摩,990 為鳳凰城,985 為圖森,980 為亞特蘭大,970 則為波士頓。

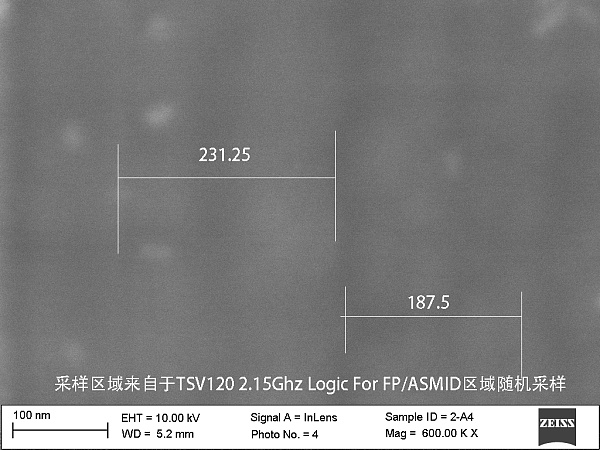

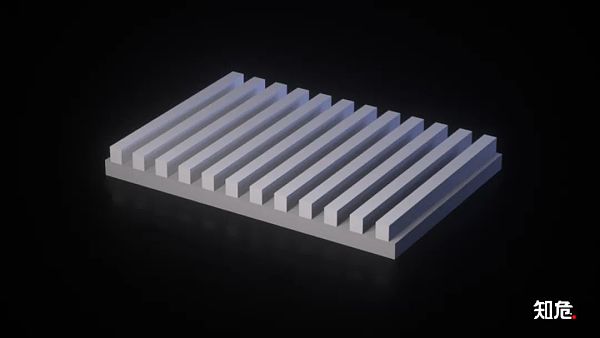

在製程上,從知危編輯部獲得的麒麟9000s 的SEM( 掃描電子顯微鏡)圖來看,麒麟9000s 的Cell Height( 標準單元高度,常用來衡量晶片製程等級)為240nm。

經過酸洗後放大60 萬倍的麒麟9000s 局部圖

2020 年,當台積電揭露自家初代7nm 低功耗高密度方案時,Cell Height 值也是240nm。

也就是說,毫無疑問,華為的麒麟9000s 達到了7nm 製程水準。

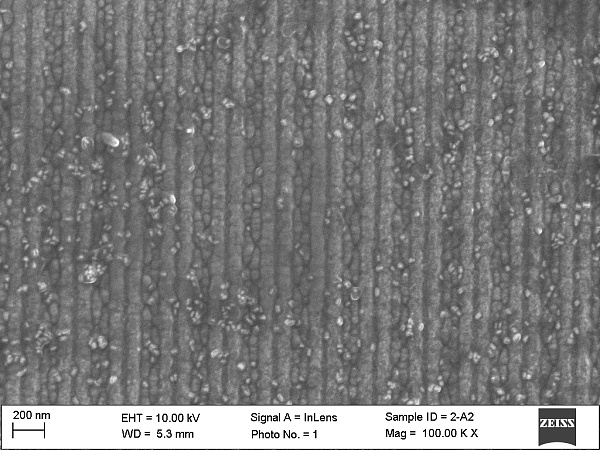

放大10 萬倍後整齊排列的麒麟9000s 電晶體

同時,知危編輯部獲得了麒麟9000s 的晶片物理結構圖,結構上,麒麟9000s 與上一代晶片麒麟9000 有非常大的差別。

所以,我們可以在這裡略帶興奮或是自豪地告訴大家:麒麟9000s 是一款全新的、並非由麒麟9000 存貨修改而來的、達到了7nm 先進製程的晶片。

吳旭告訴知危,夏洛特共有8 個核心,為三叢簇( 一種排布方式),分佈是1+3+4,主頻最高超過2600MHz,GPU 則為Maleoon 910 。

華為的5G 基頻部分一直都是以4G+5G 兩個模組、中間用巴龍基頻晶片連接的設計,這一代則沒有採用這種架橋方式,而是用一個模組整合了4G 與5G。

和麒麟9000 相比,夏洛特CPU Cluster 巨大的面積,發生了大的變化,這代的總線,不像上代的總線與超大核使用了性能庫,這代只有超大核使用了性能庫。

GPU 方面,夏洛特的Maliang 910 則是Cu 設計。其設計規模與上代相比略微縮小了一部分,為4CU 左右兩組ALU Core,每組128Alus,總計2x4x128Alus=1024Alus,頻率最高750Mhz,理論性能為1536Gflops,中間的則是GPU L2 Cache,大約為1MiByte。從其GPU的規格上來說不與常見的IMG/MALI/Adreno/Rdna/Cuda 相同。

但,眾所周知,華為不具備先進製程晶片的製造能力,所以問題來了:

在多輪制裁的情況下,華為,或者說中國廠商,是如何做出7nm晶片的?

白衣騎士

在之前,華為是比較信任台積電的,有相關人士向知危透露,當時華為高層內部曾判斷台積電斷供的可能性較低。

一方面,制裁前,雙方已經達成了生產最先進製程5nm 製程的麒麟9000 晶片的合作,正處於不斷深入合作的境地。另一方面,晶片代工錨定一家工廠製造也出於成本考量。

「 現在看來,在那個環境下,堅持把雞蛋放在一個籃子裡似乎很不明智,一旦台積電拒絕華為的流片( 試生產),就無法繼續生產,走下面的流程」 有關人士向知危表示。

2020 年5 月,來自美國升級制裁,其宣布限制使用美國技術的廠家( 如台積電)給華為代工晶片,此禁令並未立即實施,美國給出了120 天緩衝期。

2020 年7 月16 日的業績發表會上,台積電選擇了妥協,顯示9 月14 日之後,台積電將不再繼續給華為供貨晶片。

華為的反應非常迅速,在製裁發布之後,內部立刻下達了麒麟9000 的量產決定。

一般來說,海思設計的晶片要經過多次投片( 設計好後給工廠進行試生產測試),一位華為相關部門的員工向知危表示,當時麒麟9000 的決策本來是投片3 次,但是在第2 次後遇到了製裁令,所以「 第3 次沒投,直接量產了」。這些晶片,幫助華為在徹底斷供後支撐了近兩年。

2020 年10 月31 日,麒麟晶片及技術開發部內部舉辦了一場麒麟9000 的發布會,核心主題是 “ 堅定信念,永不言棄”。

受訪者供圖

但是,麒麟9000 用一片就少一片,未來的晶片麒麟9000s,由誰來打造呢?

2020 年,是個特殊的節點,中國廠商處於生死存亡時刻的不僅只有華為,還有中芯國際( SMIC )。

這年的中秋節,恰逢國慶假期,中芯國際的前員工徐勤和團隊同事突然被緊急叫到了公司,他們收到了一個令人震驚的消息:美國商務部工業與安全局( BIS )已經根據美國進出口管制條例,向中芯國際的部分供貨商發出信函,要求其對中芯國際供貨前,必須申請出口許可。

這個消息在12 月4 日才正式由美國國防部發布,公告中宣稱正式將包括中芯國際在內的四家中國企業加入「 軍事最終用戶」( Military End-User )名單。

當時的中芯國際是中國大陸最有可能躋身世界一流行列的晶片製造企業,如果無法取得境外的先進設備和原料,中芯國際的成長進度會被嚴重拖慢。

措手不及的恐慌和緊急調整的工作並行。 「上面要求每個人分析目前自己的設備,如果停了該怎麼辦?解決辦法是什麼?零件、原物料、需要國外廠商過來做服務的設備,自己能做嗎,能做多少?」徐勤回憶。

“ 最壞的打算就是完全切割,不相往來了。”

對應的,相關的美國企業也在和律師團隊解讀美政府發布的信息,但是涉及國家利益的法令,對方也只能是友好協商,立刻執行,無法越雷池半步。短期的驚慌之後,中芯國際發現,限制內容集中在高端過程所需技術和設備,「 卡脖子」 留出了一絲呼吸的契機。也因此,國產替代的步伐被推入快車道。

但,最受影響的則是中芯國際的先進製程團隊,據接近中芯國際的人士透露,內部曾有人提議先購買ASML 的EUV 光刻設備( 常用於7nm 及以下製程的設備),同時進行相關製程技術的開發。

不過,這個提議未被採納。因為當時無論是台積電還是三星,都先使用DUV 光刻來完成“ 過渡版” 的7nm 工藝,在積累了更多經驗、達到一定規模後,才導入EUV。 ( DUV 光刻機精度較EUV設備低,一般認為,「 5nm 」 製程是其的製造極限,但業界7nm 左右就會採用EUV 微影機)

另一部分原因是由於設備太昂貴,推遲了下單時間,並在後續交付不斷被卡,至今無法交付。

中芯原計劃從28 奈米向20 奈米進軍,但後來內部決定放棄20 奈米,直接進入更先進的14 奈米。並在2019 年試產良率從3% 迅速提高到95%,達到量產。

關於7nm 晶片的開發階段,我們可以從2020 年12 月梁孟松( 現任中芯國際聯合執行長)致董事會的信函中看出一二。 「 這段( 2017~2020 )期間,我盡心協力完成了28nm 到7nm,共五個世代的技術開發……目前,28nm,14nm,12nm,及n+1 等技術均已進入規模量產,7nm 技術的開發也已經完成,明年( 2021 )4 月就可以馬上進入風險量產……”

有趣的是,信中預估的風險量產時間點為2021 年4 月,這與前文中判斷的麒麟9000s 生產時間是驚人吻合的。

新的問題是,在沒有先進光刻機的情況下,中芯國際使用了哪種技術?如果量產7nm 製程在國產晶片上,會遇到哪些難題?

用刷子畫細線

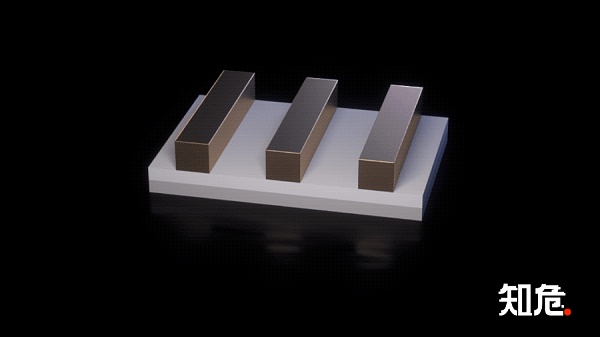

我們需要重新認識一下晶片了,薄薄的晶片其實內部可能多達百層。

晶片工藝,都是先在矽片上做出晶體管形貌,一層層沉積鍍膜,堆出上面的金屬層、隔離層、鈍化層,其中最底端的才是最核心、工藝最尖端的部分,電容和電晶體都在這裡,叫做底層元件。一般我們所指的幾奈米晶片,指的就是最下面的電晶體部分。

到了28 奈米以下,因為量子穿隧效應嚴重,會漏電,平面型電晶體無法滿足使用要求,必須把柵極像個魚鰭一樣立著包起來,做成FinFET,也就是“ 鰭式場效電晶體” 。說起來,這個創新來自華裔科學家,曾經的台積電首席技術執行長胡正明教授。

這時候立體型電晶體其實很難用長度量化,看其到達什麼製程水平,也就是俗稱的幾奈米,要看多個技術指標,例如電晶體閘極、鰭間的最小間距( Fin Pitch ),Cell Height以及電晶體密度( 晶片上每一毫米能容納多少電晶體)。

而最先進的193nm DUV 浸沒式光刻機能夠提供36~40nm 的半週期分辨率,滿足28nm 邏輯技術節點的要求。小於這個尺寸,就需要雙重甚至多重光刻技術。

多重微影技術的核心就是把原來一層光刻的圖形分割到兩個或多個遮罩上,用多次光刻和蝕刻來實現原來一層設計的圖形,使其可以蝕刻出超過單次曝光CD( Critical Dimension,指在積體電路光罩製造及光刻製程中為評估及控制製程的圖形處理精度,特設計一種反映積體電路特徵線寬度的專用線圖形)的資料。

雙重曝光被廣泛應用於22nm、20nm、16nm 和14nm 技術節點以及先進製程非關鍵層製作。但在EUV 微影機技術成熟後,台積電、三星逐漸使用EUV 微影機,這是完全不同的技術路線,只需要一次曝光就能達到效果。

中芯國際要在沒有EUV 光刻機的前提下做到7nm,可以說是用「舊技術舊機器」 達到先進目標,這有點像用鐵杵雕花。 2019 年台積電曾透過DUV 設備生產7nm 節點( N7 )晶片,後來開始使用EUV光刻機。

實現雙重甚至多重光刻的技術路線有很多種,例如LFLE 製程、LELE 製程、LELELE 製程、SADP、SAQP 技術等。

之前曾有消息指出華為可能會透過所謂的「 晶片堆疊」 技術,用兩個14nm 晶片達到7nm 晶片的效果。但一位了解晶片製程的人士告訴知危這不太可能,「 一般這種製程用於HBM( 高寬頻記憶體)的3D 封裝技術,並不是一個14+14=7 的問題,解決兩個晶片組之間的走線設計、能耗、面積等問題都有巨大的難度,用在手機晶片完全不現實。”

一位相關人士告訴知危,中芯國際是採用了SAQP 技術路線來實現7 nm 製程的。

另一位近中芯國際的人士透露,2017 年梁孟松加入中芯國際時,要求自己負責的部門技術人員全部學會SAQP 技術,“ 新入職的工程師都要加班學習這項技術。”

那麼所謂SAQP 技術是什麼呢?

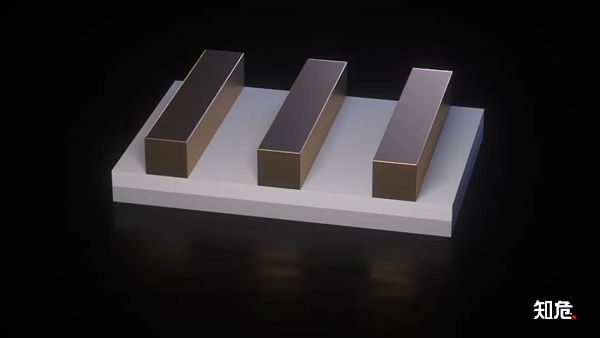

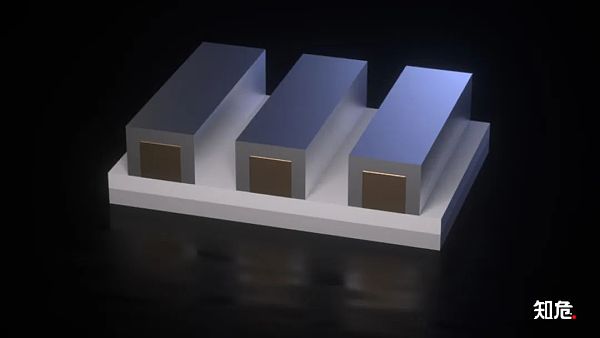

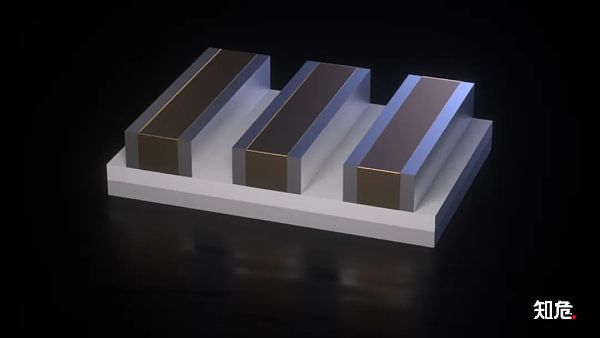

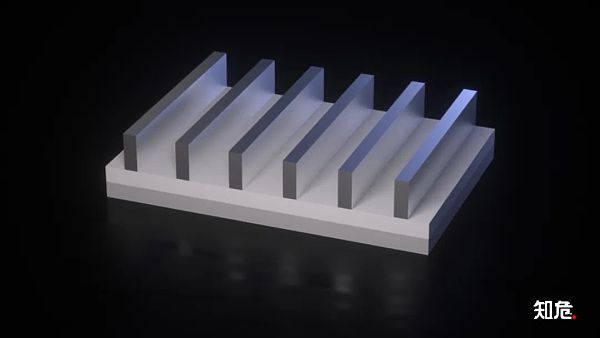

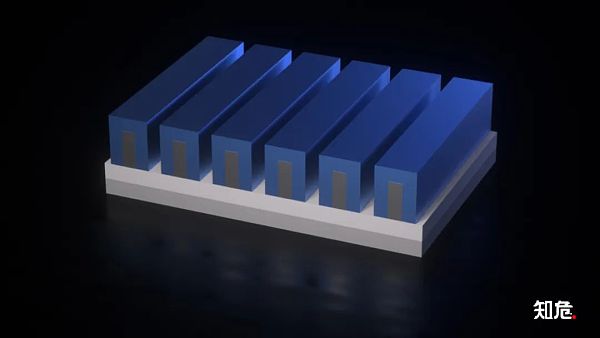

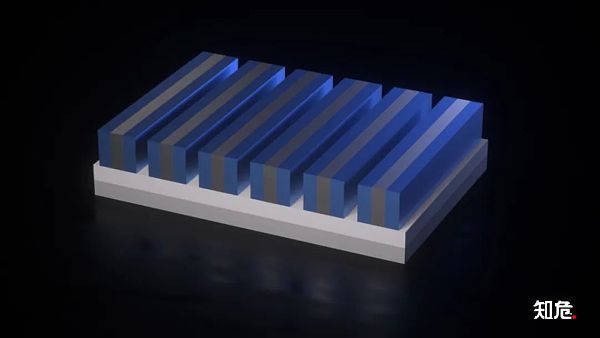

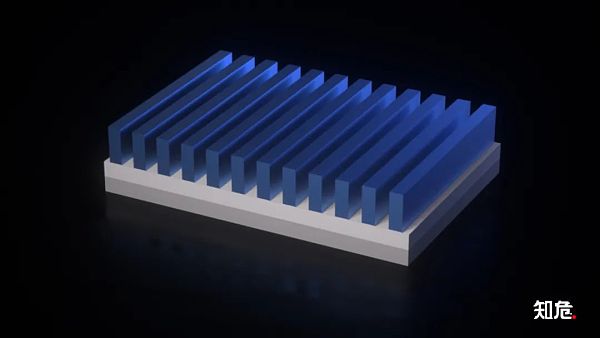

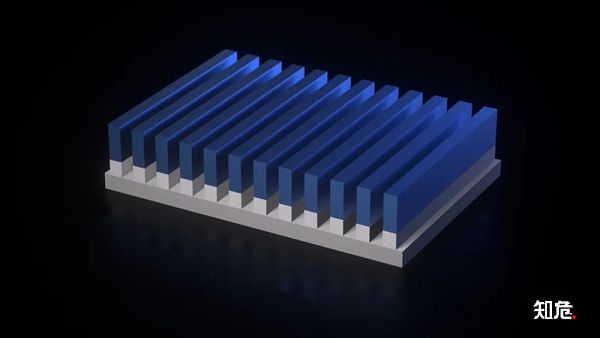

SAQP 的中文名字叫做“ 自對齊四重曝光”,它的實現原理簡單通俗來講是:

①先用光刻機畫“ 格子”,接著用蝕刻機刻出“ 格子”;

②在刻出的格子上進行化學氣相沉積鍍膜;

③用蝕刻技術去除水平面上的鍍膜,此時我們獲得了由薄膜組成的「 側壁」;

④再進行一輪蝕刻,這樣我們就獲得了由薄膜側壁組成的更密的「 格子」;

⑤再進行一次化學氣相沉積鍍膜;

⑥用蝕刻技術去除水平面上的鍍膜;

⑦再次蝕刻,獲得更加密的「 格子」;

⑧在格子的阻擋下,繼續向下蝕刻;

⑨去掉鍍膜格子,留下真正需要的「 格子」。

知危另外渲染了一張動圖,讓大家更能理解:

至此,我們利用蝕刻技術,在只擁有DUV 光刻機這把很粗的「 刷子」 情況下,畫出了細線。

其實,無論前文提到的哪一種技術理論,都已經出現了多年,但在工藝的技術選擇和節點選擇上,學習曲線會顯得極為重要,因為每跨一步都需要大量的資金和人力。

而中芯國際能完成如此高難度的事,除了關鍵技術人員,或許跟他的企業文化有關。

徐勤認為,「 服從、強執行力、在技術層面上的絕對務實」 造就了有20 餘年歷史的中芯國際。

「 明確了研發目標後,結果導向,百分之百執行,更尊重做事的人。」 據其觀察,人事的變動對於公司各項目的研發影響很少,加上強執行力,讓公司能有很好的發展。

知危了解到一個未能證實的業界傳言,中芯國際的先進製程團隊,曾經連續三年全年無休,只在一年元旦放了一天假。

而從結果來看,依照過去先進製程的時間節點計算,中芯國際的確用3 年時間,走完了其他廠商10 年的路。

合璧,良率,成敗在此一舉

相關人士向知危透露,夏洛特立項之後,一開始的代工廠就定為了中芯國際,並且這也是唯一可行的方案,當時華為處於被技術圍堵的階段,從台積電購得的先進芯片即將消耗殆盡,材料進口也受到阻礙。

值得一提的是,在麒麟9000 晶片研發時期,華為就曾在中芯國際流過片,「 但是後來沒上,不過下一代( 9000s )就是了」 一位中芯國際的員工提到。

在製裁的步步緊迫下,去A( 美)化在華為內部全面展開。 「 不只是技術上去A,辦公室軟體、專業軟體也一樣,沒有就自己做,最後達到美國產品和技術完全退出工作流程」 有前員工提到,當時有華為通訊部門直接下馬重新論證可行性。

由於無法判斷日益加緊的限制究竟有多大,在最短時間內完成夏洛特的量產就成為重中之重。雙方合作的第一步就是進行製程遷移和匹配,這往往被外界忽略。

一般來講,在先進製程上,設計方案與各家代工廠還有一道適配的過程,台積電、三星這樣的先進製程代工廠擁有專門的團隊進行“ 轉碼適配”,但是“ 中芯國際國際當時沒有這樣的設計規則遷移團隊,華為曾派駐了一支團隊進行工藝適配」 相關人士說,整個過程在3~6 個月左右。

這之後,良率就成為關鍵了。

在半導體領域,良率關乎晶片量產成本,每片晶圓上品質合格的晶片越多,晶片的成本就越低。而最終良率由每一步製程的積組成,即使假設某晶圓廠的產線上每一道製程高達99%,那麼經過500 道工序後整體良率只有0.66%,出來的完全是廢片。總的來說,良率可以細分為Wafer( 矽晶圓)良率、Die 良率和封測良率,Die 良率相對對總良率的影響較大。

相關人士告訴知危,夏洛特在風險量產的時候良率大概在35%,而一般來說,達到量產至少要到50% 以上,但這也與能達到90% 以上良率工藝成本相差一倍。

知危另外獲悉,今年,某封裝廠接到夏洛特晶片的訂單,該廠在近幾個月達到月產能400 萬片。

至於現在的真實總良率,我們不得而知,由於跟晶片成本強相關,這一般會被廠商視為秘密。

但,相關人員向知危透露,夏洛特在正式量產初期,良率已經達到了50%-60% 左右,之後的良率爬坡也相當可觀,可以支持其成本可控的大規模投產。

所以,你可以看到這樣一則新聞:華為目標在2024 年出貨6,000-7,000 萬支智慧型手機。

而在2022 年,華為智慧型手機的出貨量僅約3,000 萬支。

此時,或許我們可以長舒口氣,說一句:

輕舟已過萬重山。

後記

麒麟9000s 的成功,或許是晶片國產化的里程碑,但這只是漫漫長路上的階段性勝利。

一位半導體行業從業者擔憂地向知危表示,成果展現後,預期未來的製裁會更加猛烈,這次成功,是在製裁下有限的空間裡“ 喘了口氣”,“ 卡脖子這個事情,這次它卡在這裡,下次呢?下次可能手就伸得更深了」。

在做這篇文章時,知危很真切地感受到,技術的創新突破更多是協同作戰的結果,當一場危機撬動行業時,無法單純的去判斷這到底是一場浩劫還是置之死地而後生的機會。很多從業者都有一種莫名的「 信念」。在他們眼中,只要確定目標,務實協同,就沒有什麼完成不了的事。

我們想,這大概就是所謂的:

信念可移山。

下一代晶片,代號“ 納許維爾”,正在路上。

( 應受訪者要求,文中所涉人名均為化名)